Divisible Load Scheduling on Heterogeneous Distributed Systems

異種分散システムにおける 可分タスクのスケジューリング

July 2008

Graduate School of Global Information and Telecommunication Studies Waseda University

Audiovisual Information Creation Technology II

Abhay Ghatpande

In memory of my papa

# PREFACE

With the proliferation of the Internet, *volunteer computing* is rapidly becoming feasible and gaining popularity. Volunteer computing is a form of distributed computing in which a large number of average users offer their computers to serve as processing and storage resources for scientific research projects or what are known as *grand challenge problems*. Similarly, *grid computing* and *cloud computing*, which provide mechanisms for users and applications to submit and execute computationally intensive workflows on remote resources, are being used for wide variety of applications today.

The jobs that can be submitted to these systems are limited because they use open and shared resources that introduce three important challenges: (a) heterogeneity, (b) uncertainty, and (c) network latency and delay. If an application has a complex structure, then a lot of time is spent waiting for data to be transferred between the participating nodes. This makes *divisible loads* ideally suited for execution on volunteer and grid computing systems. Divisible loads are perfectly parallelizable and can be arbitrarily partitioned into independently and identically processable load fractions.

Divisible loads usually follow the master-slave model of computation: a master node holds the entire (divisible) load and distributes it to the slave nodes; the slave nodes perform requisite processing on the allocated load fractions, and send the results back to the master. This research considers two of the above mentioned issues: (a) the slaves are heterogeneous, i.e., they differ in computation speed and the bandwidth of the network that links them with the master node, and (b) the networks have high latency, i.e., the bandwidths can be considerably lower than the computation speeds.

Under these conditions, the focus of this research is to minimize the *makespan*, i.e., the total time from the point that the master begins sending out load fractions to the point where result collection from all slaves is complete. This involves optimizing (a) the selection of slaves to allocate load, (b) the quantity of load to be allocated to each, (c) the order (sequence) in which the fractions are sent to the slaves, and (d) the order in which the slaves send the results back to the master. This optimization problem is referred to as the DLSRCHETS (Divisible Load Scheduling with Result Collection on HETerogeneous Systems) problem.

Divisible Load Theory (DLT), the mathematical framework for the optimization of Divisible Load Scheduling (DLS) has been studied for over ten years. Most of the work has concentrated on the case where no results are returned to the master. This simplifies the analysis to a great extent, and allows for derivation of optimal load fractions and sequence of distribution to the slaves. The addition of result collection and system heterogeneity breaks down this simplicity. The complexity of DLSRCHETS is an open problem and there is no known polynomial-time algorithm for an optimal solution to DLSRCHETS. Before this research, the only proposed solutions to DLSRCHETS were FIFO (First In, First Out) and LIFO (Last In, First Out) type of schedules, which are not always optimal.

This work considers the most general form of DLSRCHETS. No assumptions are made regarding the number of slaves that are allocated load, both the network and computation speeds of the slaves are considered to be heterogeneous, and idle time can be present in the schedule if it reduces the makespan.

The overall flow of this thesis is as follows. The theoretical basis of DLSRCHETS is first established, and it is defined in terms of a linear program for analysis. The optimal schedule for a system with two slaves is extensively explored because the proposed algorithms are built on it. Two new polynomial-time algorithms, namely ITERLP (ITERative Linear Programming) and SPORT (System Parameters based Optimized Result Transfer) are proposed as solutions to DLSRCHETS. The performance of traditional and new algorithms is compared using a large number of simulations and the proposed algorithms are shown to have superior performance. The thesis is organized into five main chapters, preceded by an introduction, and terminated by a conclusion as described below.

**Chapter 1. Introduction** establishes the research context that forms the basis for this thesis. It introduces the application areas of volunteer and grid computing, and the problems faced in scheduling applications on these platforms. Next, divisible loads and divisible load scheduling are introduced along with the important results to date. The short-comings of traditional DLT and the research objectives are laid out. Traditional methods are compared with the new approaches in this thesis, and the contributions of this thesis are elaborated. The organization of the thesis is explained.

**Chapter 2. System Model** defines the system model upon which this thesis is built. There are several important constraints and assumptions that are used in the problem definition. The first one is that the communication and computation times are linearly increasing functions of the size of data. Similarly, the size of result data generated by a processor is directly proportional to the size of its allocated input load data. The constant of proportionality depends only on the application under consideration and is the same for all the processors. It is assumed that a processor can do only one thing at a time, i.e., communica-

tion and computation cannot overlap in a processor. Further, a processor can communicate with only one other processor at a time. This is known as the unidirectional one-port model. All operations including data transmission, reception, and computation follow the atomic or block-based model, i.e., they proceed uninterrupted in a single installment until the end. In this chapter, justification is given for all these assumptions considering the target applications and environment.

**Chapter 3. Analysis of DLSRCHETS** provides a detailed derivation of the DLSRCHETS problem definition. After first laying the theoretical basis, the DLSRCHETS problem is defined in terms of a linear program. The analysis of the optimal solution to DLSRCHETS is presented. Two important proofs are given — one for the *allocation precedence condition* and the other for the *idle time theorem*. The allocation precedence condition is necessary to limit the number of possible schedules of DLSRCHETS to a finite number. It argues that there always exists an optimal solution to DLSRCHETS in which the entire load is first distributed to the slaves before the master starts to receive results from the slaves. The proof uses rearrangement of the timing diagram to substantiate the claim.

The proof of the idle time theorem is more complicated as it uses the geometry of linear programming. A brief introduction to linear programming is included in the chapter for this reason. The idle time theorem states that not all slaves may be allocated load in the optimal solution, and irrespective of the number of slaves that are allocated load, at most one slave can have idle time in the optimal solution. In linear programming, some solutions can be degenerate. Analysis proves that the idle time theorem is true for both non-degenerate and degenerate cases.

**Chapter 4. The ITERLP Algorithm** proposes the new polynomial-time ITERLP algorithm. The complexity of DLSRCHETS is an open problem and finding the optimal solution is difficult. Thus, one has to resort to heuristic algorithms under the circumstances. The proposed ITERLP algorithm reduces the number of possible allocation and collection sequences to m each instead of the usual m!. The rationale behind the *pruning* of possible schedules in ITERLP is explained.

The computation cost of ITERLP is still quite high — in the worst case  $O(m^3)$  linear programs have to be solved. The simulations show that ITERLP performance is much better than LIFO and FIFO over a wide range of parameter values. The performance of the algorithm is quite stable; schedules generated by ITERLP have execution time close to the optimal in most of the cases. In the extensive simulations performed, the maximum deviation of processing time with respect to the optimal is 0.8% for 5 processors, and it takes about 3 to 5 minutes to find the schedule. As the number of processors increase, the time required to compute the solution increases. For example, it takes around 80 minutes to compute the ITERLP schedule for 65 processors. Because the expected error is low, even though computation cost is high, ITERLP allows comparison of other heuristic algorithms when it is impractical to find the optimal solution.

**Chapter 5. The Two-Slave System** lays the foundation of the two-slave system that forms the basis for the SPORT algorithm. Several important concepts are introduced in this chapter. It begins with the three types of possible optimal schedules in a two-slave system and the related derivations. This is followed by the derivation of the optimal schedule for two processors using simple if-then-else clauses. This derivation includes two important results: (a) the condition for optimality of the LIFO and FIFO schedules, which shows that whether LIFO (resp. FIFO) is faster for a two-slave system depends only on the communication speeds of the links, and (b) the condition for the existence of idle time in a FIFO schedule that shows a relationship between the presence of idle time and the computation and communication speeds of the two processors, and the type of divisible load under consideration. Next, the equivalent processor for LIFO and FIFO schedules in a two-slave system is derived. The equivalent processor enables the combination of two processors into a single virtual processor. The equivalent processor concept is extended to an arbitrary number of processors to allocate load is derived using the equivalent processor concept.

**Chapter 6. The SPORT Algorithm** introduces the SPORT algorithm as a solution to the DLSRCHETS problem. Along with the allocation and collection sequences, the SPORT algorithm finds: (a) the number of processors to use for computation, and (b) the load fractions to be allocated to the participants. The important point is that this is done without solving time-consuming linear programs. The number of possible allocation and collection sequences is limited to a few, potentially optimal permutations. Because of this, with a set of processors sorted by decreasing communication speed, the complexity of SPORT is O(m), where m is the number of available processors. The algorithm is robust to system composition and it provides good schedules for both homogeneous and heterogeneous types of systems. In the large number of simulations performed, the maximum deviation of processing time with respect to optimal is 1.5% for 5 processors. SPORT is very fast — it takes less than a second to find the solution for 500 processors.

The basic idea behind SPORT is very simple — to use two processors at a time and build a piecewise locally optimal schedule. However it is not very straightforward to be able to do this directly, and several necessary tools are designed. Detailed explanation regarding the working of the algorithm is given. The method of deriving load fractions using binary tree traversal is explained. Results of the comprehensive simulation testing of the algorithms are presented.

**Chapter 7. Conclusion** summarizes the various points covered in the thesis and presents several ideas for future work. It is proposed that future work can proceed in the following main directions: (a) Theoretical analysis of complexity and other optimality results, (b) Extensions to the current system model, (c) Modifying the nature of DLSRCHETS itself, and (d) Development of applications and physical testing.

### ACKNOWLEDGEMENTS

I express my sincere gratitude to my advisor Prof. Hiroshi Watanabe, and co-advisors, Prof. Hidenori Nakazato and Prof. Olivier Beaumont. Without their guidance and encouragement, I would have made no progress. I thank Dean Yoshiyori Urano and Prof. Wataru Kameyama, for being on the jury, and for their questions and comments on the dissertation.

I am deeply indebted to several people who helped me over the years. Some of them are Prof. Thomas Robertazzi, Prof. Veeravalli Bharadwaj, Prof. Maciej Drozdowski, Prof. Gerassimos Barlas, Prof. Jeff Erickson, Prof. Akihisa Kodate, Dr. Henning Breuer, and Dr. Jim Dowling.

My thanks to all my friends and colleagues who have enriched my life in ways too numerous to mention.

And finally, a big thank you to my family - my greatest asset. I am fortunate to be surrounded by such wonderful, supportive people.

# TABLE OF CONTENTS

| Preface i |                     |                                          |    |  |

|-----------|---------------------|------------------------------------------|----|--|

| Lis       | List of Figures xii |                                          |    |  |

| Lis       | List of Tables xiii |                                          |    |  |

| 1         | Intro               | oduction                                 | 1  |  |

|           | 1.1                 | Research Context                         | 1  |  |

|           |                     | 1.1.1 Volunteer and Grid Computing       | 1  |  |

|           |                     | 1.1.2 Divisible Loads and Scheduling     | 3  |  |

|           |                     | 1.1.3 Shortcomings of Traditional DLT    | 6  |  |

|           | 1.2                 | Research Objectives                      | 9  |  |

|           | 1.3                 | Thesis Contributions                     | 10 |  |

|           | 1.4                 | Thesis Organization                      | 13 |  |

| 2         | The                 | System Model                             | 17 |  |

|           | 2.1                 | Introduction                             | 17 |  |

|           | 2.2                 | Job Execution Model                      | 17 |  |

|           | 2.3                 | Communication and Computation Model      | 18 |  |

|           | 2.4                 | Communication and Computation Parameters | 20 |  |

|           | 2.5                 | Result Data Model                        | 21 |  |

|           | 2.6                 | Communication and Computation Time       | 21 |  |

|           | 2.7                 | Summary                                  | 23 |  |

| 3         | Anal                | lysis of DLSRCHETS                       | 25 |  |

|           | 3.1                 | Introduction                             | 25 |  |

|           | 3.2                 | Problem Formulation                      | 25 |  |

|           | 3.3                 | A Primer on Linear Programming           | 33 |  |

|           |                     | 3.3.1 General Linear Programming Problem | 33 |  |

|           |                     | 3.3.2 Geometry of Linear Programming     | 34 |  |

|   |      | 3.3.3 Bases, Feasibility, and Local Optimality    | 36 |  |  |  |

|---|------|---------------------------------------------------|----|--|--|--|

|   | 3.4  | Analysis of Optimal Solution                      | 36 |  |  |  |

|   | 3.5  | The Importance of Idle Time                       | 43 |  |  |  |

|   | 3.6  | Summary                                           | 45 |  |  |  |

| 4 | The  | ITERLP Algorithm                                  | 47 |  |  |  |

|   | 4.1  | Introduction                                      | 47 |  |  |  |

|   | 4.2  | Brief Introduction to Permutations                | 47 |  |  |  |

|   | 4.3  | Proposed Algorithm                                | 50 |  |  |  |

|   | 4.4  | Algorithm Explanation                             | 51 |  |  |  |

|   | 4.5  | Finding Candidate Sequences                       | 52 |  |  |  |

|   | 4.6  | Complexity and Discussion                         | 53 |  |  |  |

|   | 4.7  | Simulation Results and Analysis                   | 54 |  |  |  |

|   |      | 4.7.1 Algorithm Variants for Comparison           | 55 |  |  |  |

|   |      | 4.7.2 Simulation Method                           | 56 |  |  |  |

|   |      | 4.7.3 Result Plots and Analysis                   | 57 |  |  |  |

|   | 4.8  | Summary                                           | 60 |  |  |  |

| 5 | Two  | wo-Slave System 6                                 |    |  |  |  |

|   | 5.1  | Introduction                                      | 63 |  |  |  |

|   | 5.2  | Two-Slave System Configuration                    | 64 |  |  |  |

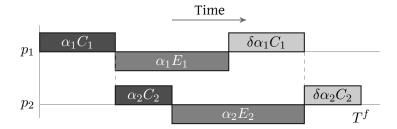

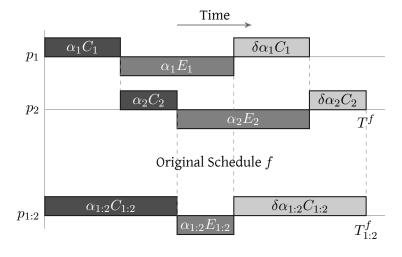

|   | 5.3  | Schedule $f$                                      | 67 |  |  |  |

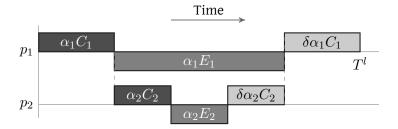

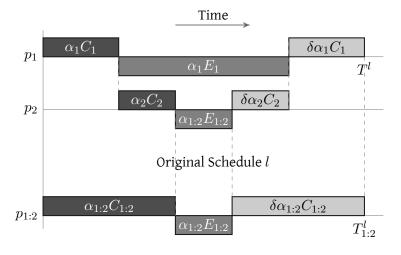

|   | 5.4  | Schedule <i>l</i>                                 | 69 |  |  |  |

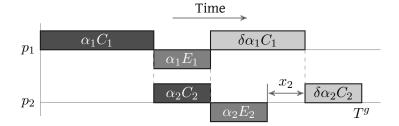

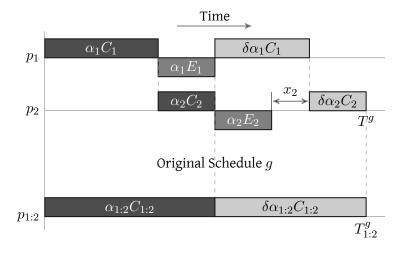

|   | 5.5  | Schedule $g$                                      | 72 |  |  |  |

|   | 5.6  | Optimal Schedule in Two-Slave System              | 74 |  |  |  |

|   | 5.7  | The Concept of Equivalent Processor               | 76 |  |  |  |

|   | 5.8  | Equivalent Processor for Schedule $f$             | 77 |  |  |  |

|   | 5.9  | Equivalent Processor for Schedule $l$             | 78 |  |  |  |

|   | 5.10 | Equivalent Processor for Schedule $g$             | 79 |  |  |  |

|   | 5.11 | The Equivalent Processor Theorem                  | 79 |  |  |  |

|   | 5.12 | Extending the Equivalent Processor Concept        | 82 |  |  |  |

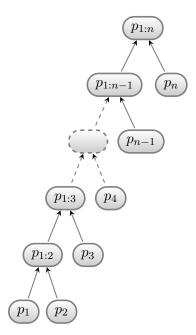

|   |      | 5.12.1 The General FIFO Schedule                  | 83 |  |  |  |

|   |      | 5.12.2 General FIFO Equivalent Processor          | 84 |  |  |  |

|   |      | 5.12.3 The General LIFO Schedule                  | 86 |  |  |  |

|   |      | 5.12.4 General LIFO Equivalent Processor          | 87 |  |  |  |

|   |      | 5.12.5 Results Using General Equivalent Processor | 88 |  |  |  |

|   | 5.13 | Summary                                           | 89 |  |  |  |

| 6              | The SPORT Algorithm91          |         |                                                                                   | 91  |

|----------------|--------------------------------|---------|-----------------------------------------------------------------------------------|-----|

|                | 6.1 Introduction               |         |                                                                                   | 91  |

|                | 6.2 Proposed Algorithm         |         |                                                                                   | 92  |

|                | 6.3                            | Algori  | thm Explanation                                                                   | 95  |

|                | 6.4 Complexity and Discussion  |         |                                                                                   | 99  |

|                | 6.5                            | Simula  | ation Set A                                                                       | 100 |

|                |                                | 6.5.1   | Set $A1 - C$ homogeneous, $\mathcal{E}$ homogeneous $\ldots \ldots \ldots \ldots$ | 101 |

|                |                                | 6.5.2   | Set $A2 - C$ homogeneous, $\mathcal{E}$ heterogeneous                             | 103 |

|                |                                | 6.5.3   | Set A3 – $C$ heterogeneous, $E$ homogeneous                                       | 105 |

|                |                                | 6.5.4   | Set A4 – $C$ heterogeneous, $E$ heterogeneous                                     | 106 |

|                |                                | 6.5.5   | Simulation Result Analysis                                                        | 108 |

|                | 6.6 Simulation Set B           |         |                                                                                   | 111 |

|                |                                | 6.6.1   | Simulation Method                                                                 | 111 |

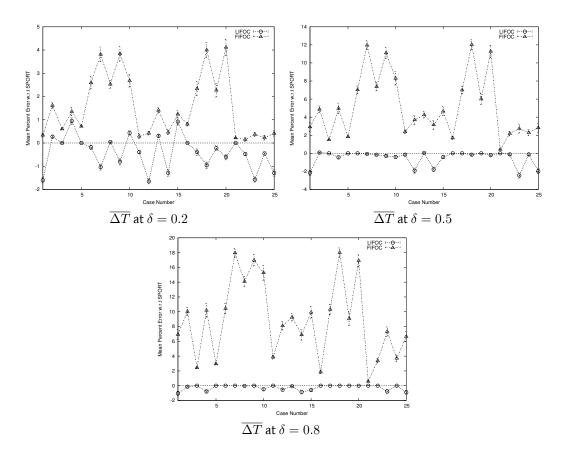

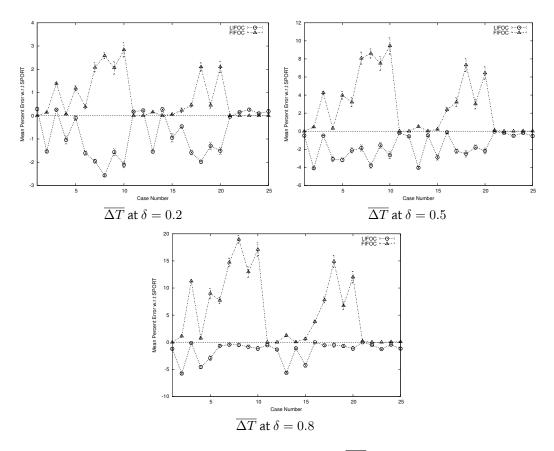

|                |                                | 6.6.2   | Simulation Results and Analysis                                                   | 111 |

|                |                                | 6.6.3   | Discussion on Performance of LIFOC and SPORT                                      | 113 |

|                | 6.7                            | Summ    | nary                                                                              | 115 |

| 7              |                                |         |                                                                                   | 117 |

|                |                                |         |                                                                                   | 117 |

|                | 7.2 Ideas for Future Work      |         | 120                                                                               |     |

|                |                                | 7.2.1   | Theoretical Analysis                                                              | 120 |

|                |                                | 7.2.2   | Extending the System Model                                                        | 120 |

|                |                                | 7.2.3   | Modification of DLSRCHETS                                                         | 120 |

|                |                                | 7.2.4   | Application Development                                                           | 121 |

| References 123 |                                |         | 123                                                                               |     |

| Li             | st of I                        | Publica | tions                                                                             | 131 |

| Ac             | Acronyms and Abbreviations 133 |         |                                                                                   | 133 |

| Li             | List of Symbols 135            |         |                                                                                   | 135 |

# LIST OF FIGURES

| 1.1  | A heterogeneous master-slave system                                                           | 3  |

|------|-----------------------------------------------------------------------------------------------|----|

| 1.2  | Divisible load partitioning                                                                   | 5  |

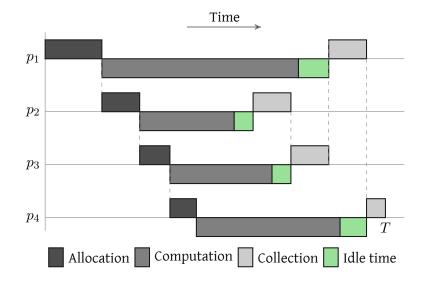

| 1.3  | The timing diagram for AFS policy                                                             | 6  |

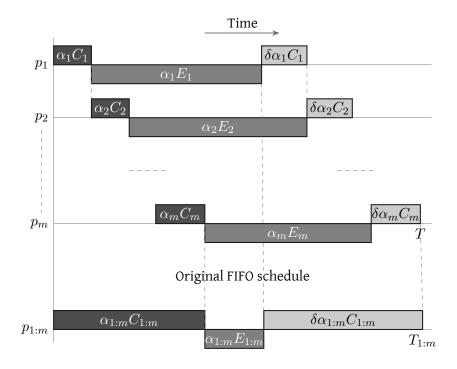

| 1.4  | Timing diagram for FIFO schedule                                                              | 7  |

| 1.5  | Timing diagram for LIFO schedule                                                              | 8  |

| 1.6  | A possible schedule in this research                                                          | 10 |

| 2.1  | A general schedule for DLSRCHETS                                                              | 18 |

| 2.2  | The heterogeneous master-slave system ${\cal H}$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21 |

| 3.1  | A possible schedule with $m=3$                                                                | 27 |

| 3.2  | Interleaved result collection                                                                 | 28 |

| 3.3  | A schedule that satisfies the Feasible Schedule Theorem                                       | 31 |

| 3.4  | Timing diagram for the optimal LIFO schedule                                                  | 40 |

| 3.5  | The rearranged optimal LIFO schedule                                                          | 41 |

| 3.6  | Timing diagram for an optimal FIFO schedule                                                   | 42 |

| 3.7  | An optimal FIFO schedule with idle time                                                       | 42 |

| 3.8  | Optimal LIFO schedule for Example 3.1                                                         | 44 |

| 3.9  | Optimal FIFO schedule with idle time in both processors                                       | 45 |

| 3.10 | Optimal FIFO schedule with idle time in one processor                                         | 45 |

| 4.1  | A feasible schedule for $m=3$                                                                 | 49 |

| 4.2  | ITERLP progress illustrated for 4 processors                                                  | 51 |

| 4.3  | Normalized Execution Time for $m=4, \delta=0.2$ , Case 9                                      | 57 |

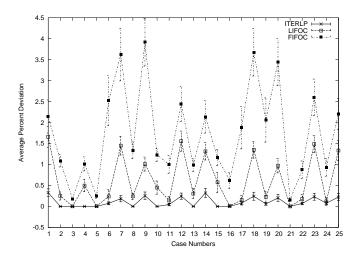

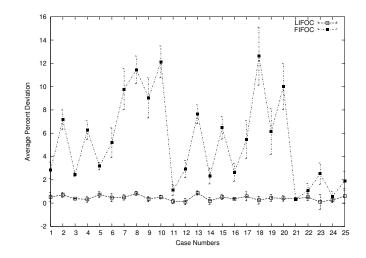

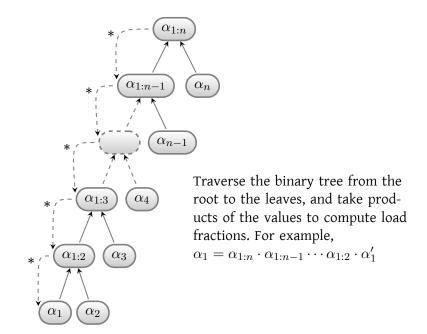

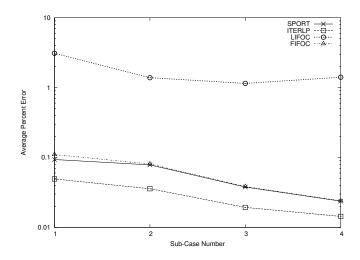

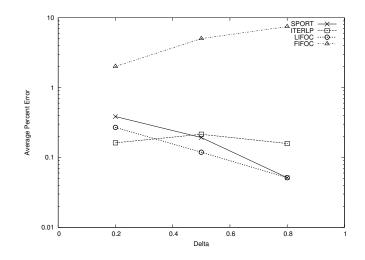

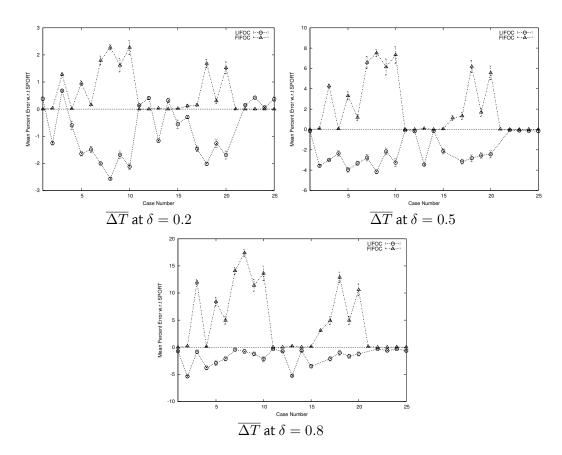

| 4.4  | $\langle \Delta T \rangle$ for $m=4, \delta=0.2$                                              | 58 |

| 4.5  | $\langle \Delta T \rangle$ for $m=5, \delta=0.8$                                              | 59 |

| 4.6  | $\langle \Delta T \rangle$ for $m = 5, \delta = 0.5$                                          | 59 |

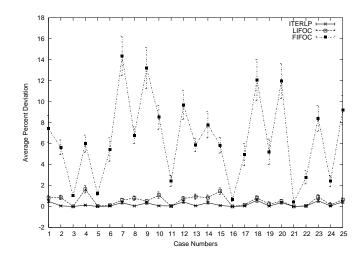

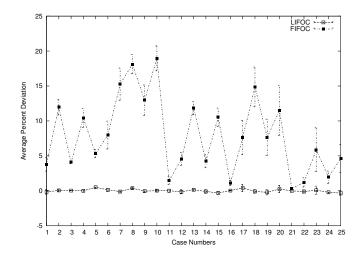

| 4.7  | $\langle \Delta T  angle$ w.r.t. ITERLP, $m=10, \delta=0.2$                                   | 60 |

| 4.8  | $\langle \Delta T  angle$ w.r.t. ITERLP, $m=20, \delta=0.5$                                   | 61 |

| 4.9  | $\langle \Delta T  angle$ w.r.t. ITERLP, $m=30, \delta=0.8$                                   | 61 |

| 4.10 | $\langle \Delta T  angle$ w.r.t. ITERLP, $m=30, \delta=0.2$          | 62  |

|------|----------------------------------------------------------------------|-----|

| 5.1  | A feasible schedule for $m = 3$                                      | 65  |

| 5.2  | A heterogeneous two-slave system                                     | 66  |

| 5.3  | Timing diagram for Schedule $f$                                      | 67  |

| 5.4  | Timing diagram for Schedule $l$                                      | 69  |

| 5.5  | Timing diagram for Schedule $g$                                      | 72  |

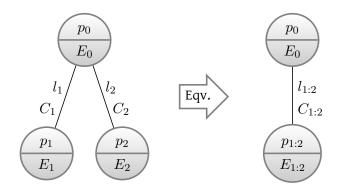

| 5.6  | The concept of equivalent processor                                  | 76  |

| 5.7  | Equivalent processor in Schedule $f$                                 | 78  |

| 5.8  | Equivalent processor in Schedule $l$                                 | 79  |

| 5.9  | Equivalent processor in Schedule $g$                                 | 80  |

| 5.10 | General FIFO schedule and equivalent processor                       | 83  |

| 5.11 | General LIFO schedule and equivalent processor                       | 86  |

| 6.1  | The SPORT Algorithm                                                  | 96  |

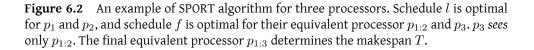

| 6.2  | An example of SPORT for three processors                             | 97  |

| 6.3  | Calculating the load fractions in SPORT                              | 98  |

| 6.4  | The main and sub-intervals used for Simulation Set A                 | 102 |

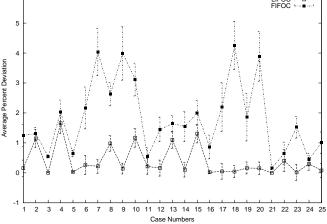

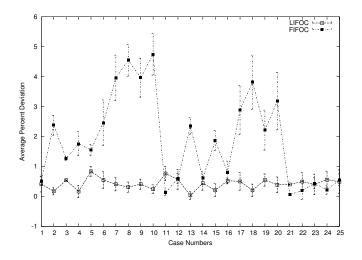

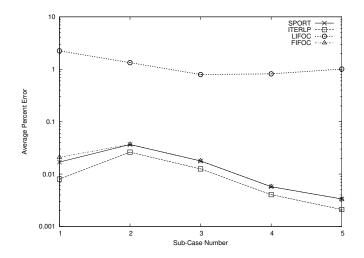

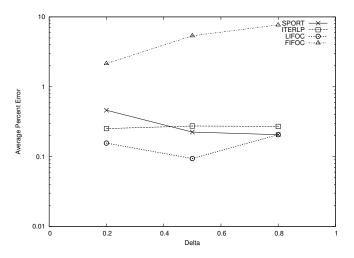

| 6.5  | $\langle \overline{\Delta T}  angle$ in Set A1 for $m=4, \delta=0.2$ | 103 |

| 6.6  | $\langle \overline{\Delta T}  angle$ in Set A1 for $m=5, \delta=0.8$ | 104 |

| 6.7  | $\langle \overline{\Delta T}  angle$ in Set A2 for $m=4, \delta=0.5$ | 105 |

| 6.8  | $\langle \overline{\Delta T}  angle$ in Set A2 for $m=5, \delta=0.2$ | 105 |

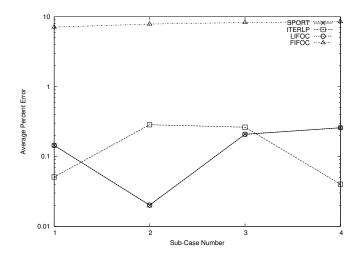

| 6.9  | $\langle \overline{\Delta T}  angle$ in Set A3 for $m=4, \delta=0.8$ | 106 |

| 6.10 | $\langle \overline{\Delta T}  angle$ in Set A3 for $m=5, \delta=0.5$ | 107 |

| 6.11 | $\langle \overline{\Delta T}  angle$ in Set A4 for $m=4$             | 108 |

| 6.12 | $\langle \overline{\Delta T} \rangle$ in Set A4 for $m=5$            | 108 |

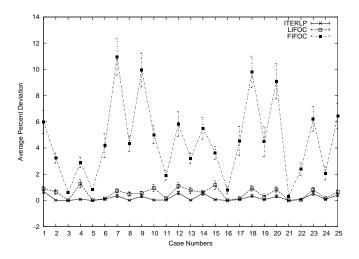

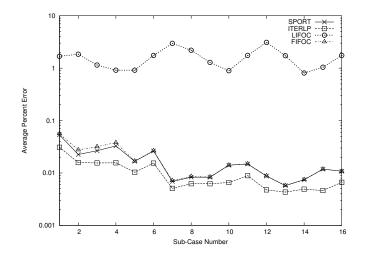

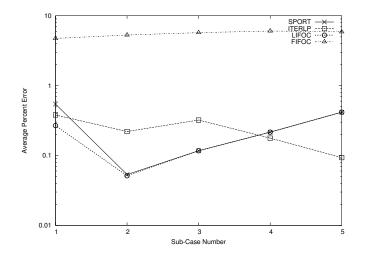

| 6.13 | $\overline{\Delta T}$ in simulation set B, $m=10$                    | 112 |

| 6.14 | $\overline{\Delta T}$ in simulation set B, $m=100$                   | 113 |

| 6.15 | $\overline{\Delta T}$ in simulation set B, $m=300$                   | 114 |

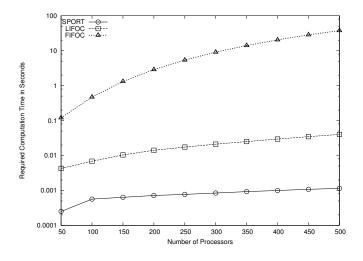

| 6.16 | Comparison of wall-clock time for SPORT, LIFOC, and FIFOC            | 116 |

# LIST OF TABLES

| 1.1 | Comparison with traditional DLS without result collection                         | 11  |

|-----|-----------------------------------------------------------------------------------|-----|

| 1.2 | Comparison with traditional DLS with result collection                            | 11  |

| 4.1 | Results for $C = \{10, 15\}, E = \{10, 10\}, \delta = 0.5$                        | 53  |

| 4.2 | Results for $C = \{10, 15, 20\}$ , $\mathcal{E} = \{10, 10, 1\}$ , $\delta = 0.5$ | 54  |

| 4.3 | Parameters for ITERLP simulations                                                 | 56  |

| 4.4 | Maximum $\langle \Delta T  angle$ of FIFOC $\ldots$                               | 58  |

| 4.5 | Maximum $\langle \Delta T  angle$ of LIFOC $\ldots$                               | 58  |

| 4.6 | Maximum $\langle \Delta T \rangle$ of ITERLP                                      | 60  |

| 6.1 | Parameters for SPORT simulation sets A and B                                      | 101 |

| 6.2 | Minimum statistics for SPORT simulation set A                                     | 109 |

| 6.3 | Maximum statistics for SPORT simulation set A                                     | 110 |

| 6.4 | Statistics for LIFOC in simulation set B                                          | 115 |

| 6.5 | Comparison of wall-clock time for SPORT, LIFOC, and FIFOC                         | 115 |

| 7.1 | Algorithm feature and performance comparison                                      | 118 |

# CHAPTER 1

## INTRODUCTION

## 1.1 RESEARCH CONTEXT

Parallel and distributed computing has been a topic of active research for over 50 years. The basic idea behind parallel computing is very simple — the simultaneous use of multiple computing elements to solve a computational problem. The primary reasons for using parallel computing are:

- To solve problems faster, i.e., save time

- To solve larger problems

- To solve several problems at the same time

There are other secondary reasons, such as economic benefits, technology limitations on serial computing, memory constraints of single computers, and availability of cheap, off-the-shelf (COTS) hardware.

The computing elements in parallel computing may be a single computer with multiple processors (these days *multiple cores* in a single CPU are also common), or several computers connected by a network, or usually a combination of both. The application under consideration decides the choice of architecture, i.e., the level at which parallelism can be most efficiently exploited as dictated by the algorithm. In this thesis, the focus is on *wide area distributed computing*, in which the computers are *loosely-coupled* and geographically dispersed. Parallelism follows the *data-parallel* model, and individual computers independently run entire programs on their share of the data.

#### 1.1.1 Volunteer and Grid Computing

With the proliferation of the Internet, *volunteer computing* [3–5] is rapidly becoming feasible and gaining popularity. Volunteer computing is a form of distributed computing

in which a large number of average users offer their computers to serve as processing and storage resources for scientific research projects or what are known as *Grand Challenge Problems* such as [93]:

- astronomy and astrophysics,

- biological, human genome,

- chemical and nuclear reactions,

- cryptography,

- geological, seismic activity,

- weather and climate study.

Similarly, *grid computing* [43, 44] and *cloud computing* [72, 96], which are new distributed computing paradigms, provide mechanisms for users and applications to submit and execute computationally intensive workflows on remote resources. Grids are being used for a large number of applications today such as:

- astronomy & space exploration [50, 90],

- distributed video capture, storage and retrieval [31],

- distributed image processing [80, 89],

- polygon rendering for simulation and visualization [58, 67],

- satellite data processing [91],

- computer vision [89],

- medical simulation [19], and many more.

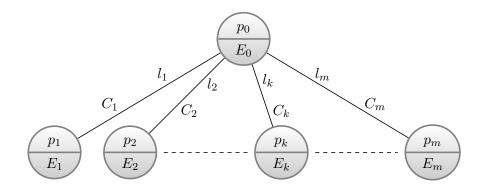

All these systems essentially follow the *master-slave* approach shown in Fig. 1.1. It is a star connected (single-level tree) network where the center of the star (root of the tree) forms the master and the points of the star (leaf nodes of the tree) form the slaves. The master holds all the data associated with a job (problem) that has to be processed in some manner. The data is then divided into a number of parts, and distributed to the slaves. The slaves perform the requisite computation on their respective parts in parallel, and return the computed results back to the master.

Because of the use of open and shared resources, one of the biggest problems faced by these new forms of distributed computing is the network latency and delay. This places a

**Figure 1.1** A heterogeneous master-slave system. Slaves can have different computing speeds and the network links connecting them to the master can have different bandwidths.

limitation on the types of jobs that can be submitted to these systems, if the systems are to be used efficiently. If an application has complex structure, then a lot of time is spent just waiting for data to be transferred between the participating nodes.

Volunteer computing uses anonymous contributed resources, and a large degree of heterogeneity exists in the network bandwidth and processing power of the participating nodes. In the case of grid or cloud computing, usually the resources are contributed by institutions, but here too, the resources are highly heterogenenous and shared among many users.

The geographical distribution of computing capabilities and the resource heterogeneity requires novel approaches to access, transfer, and process data. The basic technology for exploiting computational grids is grid middleware, which is provided by toolkits such as Globus [43], Legion [51], and UNICORE [76], and for volunteer computing by software such as BOINC [2]. These middleware toolkits offer information infrastructure services for security, communication, fault detection, resource and data management, and portability. The availability of these basic services permits the focus on algorithms for improving the utilization and efficiency of the system without worrying about *how* the implementation will be carried out.

### 1.1.2 Divisible Loads and Scheduling

Scheduling has been an important area of study for a long time. Scheduling is one of the main areas of contemporary mathematics as a branch of combinatorial optimization [87]. The origin of scheduling lies in the operations research mainly in production

and project management [6, 30, 40]. As the complexity of computer systems grew, the results from these areas were applied to the management and control of computer systems. Scheduling is now an important part of the design of libraries and compilers [7, 71, 83], operating systems [41, 88], and real-time systems [53, 79, 81, 86, 102]. Scheduling theory and its range of theoretical and practical results is too vast to be presented here. There is however one branch of scheduling theory that has gained wide importance over the last few years and that has been studied extensively for its simplicity and tractability — *Divisible Load Theory* (DLT) and *Divisible Load Scheduling* (DLS).

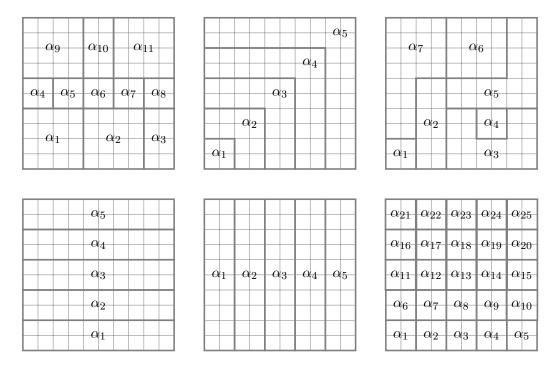

*Divisible loads* are a special class of parallelizable applications that have very regular linear structure, and which if given a large enough volume, can be *arbitrarily* partitioned into any number of independently and identically processable *load fractions* (parts). In Fig. 1.2, each light gray square represents a unit task and the set of 100 such squares represents the divisible load. As seen in Fig. 1.2, the divisible load (job) can be partitioned in any number of ways. Each part undergoes the same processing as the others, and can be processed independently of the others. The shape of a part is not important, and the partitioning of a divisible load should not be confused with a 2-dimensional cutting problem [29]. Figure 1.2 just illustrates that a divisible load is composed of independent tasks that can be clustered together arbitrarily.

Examples of applications that satisfy this divisibility property include massive dataset processing, image processing and rendering, signal processing, computation of Hough transforms, tree and database search, Monte Carlo simulations, computational fluid dynamics, and matrix computations. Divisible loads are especially suited for execution on volunteer, grid and cloud computing systems because of the absence of interdependencies and precedence relations between the different parts into which the load is divided.

The partitioning of a divisible load, the allocation (mapping) of the parts to appropriate processors for execution, and the sequencing (ordering) of the transfer of the parts to and from the processors, is together known as Divisible Load Scheduling. Divisible Load Theory is the mathematical framework that has been established to study the optimization of DLS [9, 11–13, 22–27, 34, 36, 48, 49, 56, 62, 63, 65, 73–75, 84, 85].

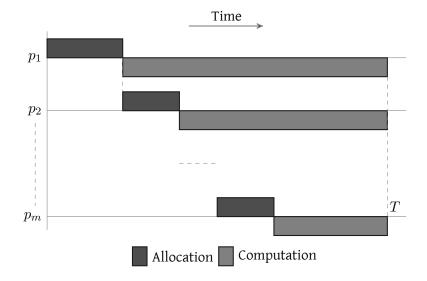

The hallmark of DLT has been its relative simplicity and deterministic nature. The basic principle of DLT to determine an optimal schedule for the master-slave system in Fig: 1.1 is the AFS (All slaves Finish Simultaneously) policy [9]. This states that the optimal schedule is one in which the load is distributed such that all the nodes involved in the computation finish processing their individual load fractions at the same time [52]. It is illustrated in Fig. 1.3 that shows the timing diagram of the slaves' communication and computation. The time spent in communication with the master is shown above the horizontal axes, and the time spent in computation by the individual slaves is shown below

**Figure 1.2** The data set associated with a divisible load (job) can be arbitrarily partitioned in any number of ways. Each part undergoes the same processing as the others, and can be processed independently of the others. The shape of the part is not important. The figure just illustrates that a divisible load is composed of independent tasks that can be clustered together arbitrarily.

the horizontal axes. This convention is followed throughout this thesis. As can be seen, all the slaves finish their computation at time T.

Blazewicz and Drozdowski [28] revised the traditional system model with overhead factors, while Bharadwaj et al. [26] extended the study with closed-form solutions for optimal processing time. Sohn et al. [85] used the DLT to minimize total monetary cost when utilizing system resources. There are several papers that have tackled other implementation related issues. For example, Li et al. [63] dealt with finite size buffer constraints which are very important when considering shared resources. Another issue is the granularity of the input load, i.e., the fact that practical loads are not infinitely divisible but have a certain minimum size. Bharadwaj and Viswanadham [21] analyzed bus networks by introducing a *divisibility factor* and dividing the load in integral multiples of the factor. Several other issues such as processor release times, multi-installment load distribution, faulttolerance, and start-up costs have been addressed in [23, 101, 104]. Some other important papers in the DLT area are [9, 11–13, 22, 23, 25, 26, 34, 36, 48, 49, 56, 62, 65, 74, 84, 85]. The definitive reference for this field is the book by Bharadwaj et al. [24], while Drozdowski [39] offers some excellent insights into the practical implementation of DLT on various

**Figure 1.3** The timing diagram for AFS policy. All processors finish their computation at the same time *T*. This is the optimal schedule when there is no result collection phase.

architectures. Bharadwaj et al. [27] and Beaumont et al. [15] recently published reviews of the work done to date in DLT. An exhaustive listing of papers regarding DLT and DLS is available on Thomas Robertazzi's homepage [73].

#### 1.1.3 Shortcomings of Traditional DLT

The AFS policy yields closed-form equations to determine the optimal load fractions to be allocated to the processors, and allows easy theoretical analysis of the system performance. The AFS policy implies that after the nodes finish computing their individual load fractions, no results are returned to the source. This is an unrealistic assumption for most applications on volunteer and grid computing, as the result collection phase contributes significantly to the total execution time. This is a serious shortcoming of traditional DLT.

Along with the AFS policy, there are two assumptions that have implicitly pervaded DLT literature to date:

- (a) Load is allocated to all available processors (slaves), and

- (b) A processor is never idle except for the time when it is waiting for the reception of its allocated load fraction from the master.

The presence of idle time in the optimal schedule has been overlooked in DLT work on result collection and heterogeneity. It is a very important issue because it may sometimes be possible to improve a schedule by inserting idle time.

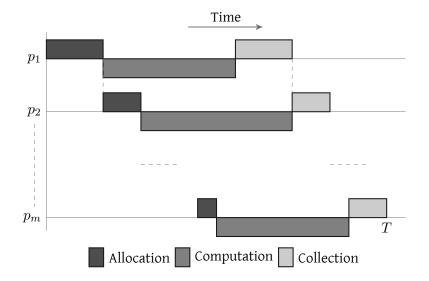

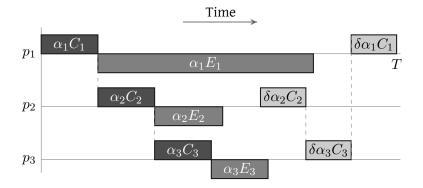

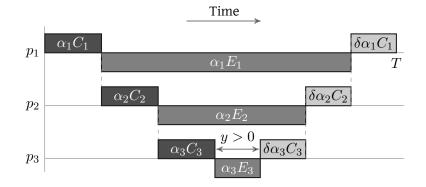

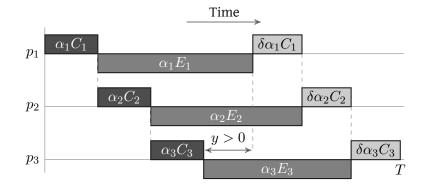

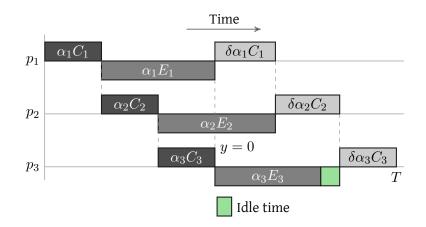

**Figure 1.4** Timing diagram for FIFO schedule. The results are collected in the same sequence as the load fractions are allocated. Though not shown in this figure, optimal FIFO schedules may have idle time.

A few papers have dealt with DLS on heterogeneous systems to date [16–18, 24, 36, 77]. Bharadwaj et al. [24], Chap. 5 proved that the sequence of allocation of data to the processors is important in heterogeneous networks. Without considering result collection, they proved that for optimum performance,

- (a) when processors have equal computation capacity, the optimal schedule results when the fractions are allocated in the order of decreasing communication link capacity, and

- (b) when communication capacity is equal, the data should be allocated in the order of decreasing computation capacity.

As far as can be judged, no paper has given a satisfactory solution to the scheduling problem where both the network bandwidth and computation capacities of the slaves are different, and the result transfer to the master is explicitly considered.

Cheng and Robertazzi [34] and Bharadwaj et al. [24], Chap. 3 addressed the issue of result collection with a simplistic constant result collection time, which is possible only for a limited number of applications on homogeneous networks. All other papers that have addressed result collection to date, advocated FIFO (First In, First Out) and LIFO (Last In, First Out) type of schedules. As shown in Fig. 1.4, in FIFO, results are collected in the same order as that of load allocation, while in LIFO, the order of result collection is reversed as shown in Fig. 1.5. Barlas [9] addressed the result collection phase for single-level and

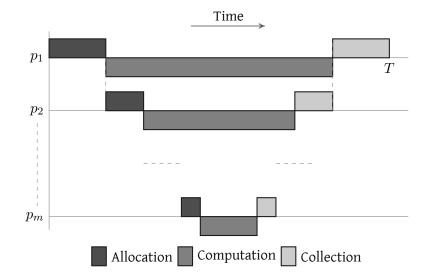

**Figure 1.5** Timing diagram for LIFO schedule. The results are collected in the reverse sequence as allocation of load fractions. In the optimal LIFO schedule, no processor has idle time.

arbitrary tree networks, but an assumption regarding the absence of idle time was made without justification. Essentially he analyzed only two cases:

- (a) when communication time is zero, and

- (b) when communication networks are homogeneous.

The optimal sequences derived were essentially LIFO or FIFO. Rosenberg [77] too proposed the LIFO and FIFO sequences for result collection. He concluded through simulations that FIFO is better when the communication network is homogeneous with a large number of processors, while LIFO is advantageous when the network is heterogeneous with a small number of processors.

For the first time, it was shown in [17] that the LIFO and FIFO orderings are not always optimal for a given set of processors. In [16, 18], it was proved that all processors from a given set of processors may not be used in the optimal solution. For the unidirectional single-port communication model (see Chapter 2), [16–18] proved the following features in optimal schedules:

- In optimal LIFO and FIFO schedules, load is allocated in the order of decreasing communication link bandwidth.

- In the optimal LIFO schedule, no processor has idle time.

- There exists an optimal FIFO schedule in which at most one processor may have idle time.

• If there exists a processor with idle time in an optimal FIFO schedule, then it can always be chosen to be the last processor in the allocation sequence (i.e. the processor with the slowest communication link).

The above optimality results have been derived strictly for LIFO and FIFO type of schedules, and are not applicable for the general case considered in this thesis.

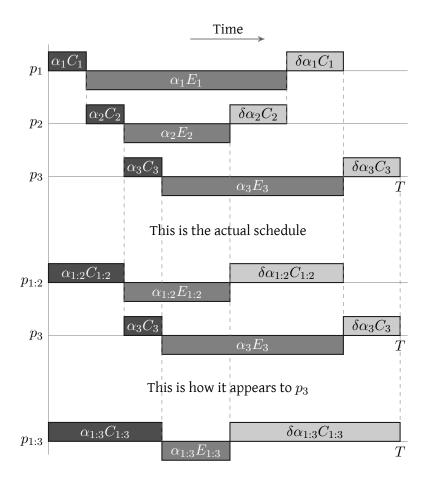

### 1.2 RESEARCH OBJECTIVES

The focus of this research is to study the scheduling of divisible loads on heterogeneous master-slave systems when the slaves return result data to the master. Specifically, it seeks to minimize the *makespan* of such a schedule, i.e., to minimize the total time from the point that the master begins sending out load fractions to the point where result collection from all slaves is complete. This involves optimizing

- (a) the selection of slaves to allocate load,

- (b) the quantity of load to be allocated to each,

- (c) the order (sequence) in which the fractions are sent to the slaves, and

- (d) the order in which the slaves send the results back to the master.

This optimization problem is called the Divisible Load Scheduling with Result Collection on HETerogeneous Systems (DLSRCHETS) problem, and it is formally defined and analyzed in detail in this thesis. The most general form of DLSRCHETS is considered. No assumptions are made regarding the number of slaves that are allocated load, both the network and computation speeds of the slaves are assumed to be heterogeneous, and idle time can be present in the schedule if it reduces the makespan.

Finding an optimal solution to DLSRCHETS is surprisingly difficult. In fact, the complexity of DLSRCHETS is an open problem and there is no known polynomial-time algorithm for an optimal solution to DLSRCHETS. Thus it is important to find some characteristics of DLSRCHETS and to gain insight into the optimal solution. Some of the questions that are addressed in this thesis are:

- How can the general DLSRCHETS problem be defined mathematically? What are the necessary conditions to be able to do that?

- Should all slaves be allocated load first before they start sending results back to the source in the optimal solution?

- Will all available slaves be allocated load in the optimal solution?

**Figure 1.6** A possible schedule in this research. Allocation and collection sequences can be arbitrary. Idle time may be present in all participating processors if it helps reduce the total processing time T.

- How many slaves that are allocated load will have idle time in the optimal solution?

- Is it possible to identify some relationship between system computation and communication speeds and the optimal solution? Under what circumstances is a particular schedule optimal? What causes it to be optimal?

- If finding an optimal solution is difficult, is it possible to find some near-optimal heuristic algorithms to solve DLSRCHETS?

Tables 1.1 and 1.2 summarize the differences between traditional divisible load scheduling and this research.

### 1.3 THESIS CONTRIBUTIONS

Several original and unique contributions resulted from the work on this thesis:

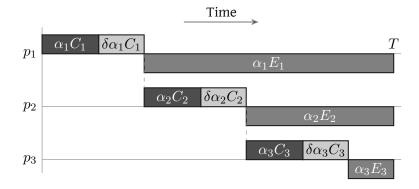

**The Allocation Precedence Lemma (Chapter 3)** The allocation precedence condition states that, *the master distributes load to all participating slaves first, before receiving any results.* The allocation precedence lemma proves that in the general case considered in this thesis, there always exists an optimal schedule that satisfies the allocation precedence condition. This is necessary to limit the range of optimal solutions to DLSRCHETS to a finite number.

**The Idle Time Theorem (Chapter 3)** A proof is given for the Idle Time Theorem, which states that, *there exists an optimal solution for DLSRCHETS in which, irrespective of whether load*

**Table 1.1**Salient features of this research as compared to traditional DLS without resultcollection. The theorems in traditional DLS are not applicable to this research.

| DLS without result collection                                                                                                            | This Research                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Ignores result collection.                                                                                                               | Explicitly schedules result collection phase.                                                           |

| <b>Theorem</b> Optimal schedule uses all available processors.                                                                           | Selects only necessary number of processors.                                                            |

| <b>Theorem</b> Optimal allocation sequence<br>is in order of decreasing communication<br>bandwidth irrespective of computation<br>speed. | Optimal sequence depends on both com-<br>munication and computation speeds; it<br>cannot be predefined. |

| <b>Theorem</b> No processor has idle time in the optimal schedule.                                                                       | <b>Theorem</b> There is an optimal solution where only one processor may have idle time.                |

**Table 1.2** Salient features of this research as compared to traditional DLS with resultcollection. This research is distinctly more general in nature. The theorems for LIFO andFIFO are not applicable here.

| DLS with result collection                                                                                                      | This Research                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Considers only LIFO or FIFO                                                                                                     | Considers completely general schedule                                                              |

| <b>Theorem</b> Optimal schedule uses all available processors.                                                                  | Selects only necessary number of processors.                                                       |

| <b>Theorem</b> Optimal allocation sequence is in order of decreasing communication bandwidth irrespective of computation speed. | Optimal order depends on both communi-<br>cation & computation speeds; it cannot be<br>predefined. |

| Usually ignores idle time. Recently consid-<br>ered idle time in FIFO.                                                          | Considers idle time to reduce makespan in some cases.                                              |

| <b>Theorem</b> There is an optimal FIFO sched-<br>ule where only one processor may have idle<br>time.                           | <b>Theorem</b> There is an optimal schedule where only one processor may have idle time.           |

is allocated to all available slaves, at most one of the slaves allocated load has idle time, and that the idle time exists only when the result collection begins immediately after the completion of load distribution. This is one of the principal contributions of this thesis. First, because it shows that in some cases insertion of idle time can be beneficial, and second, because it enables the definition of a constraint on the number of processors to be used in the SPORT algorithm.

**The ITERLP Algorithm (Chapter 4)** The new ITERLP (ITERative Linear Programming) algorithm is proposed and found to be near-optimal after rigorous testing. The ITERLP algorithm does not necessarily use all processors (slaves) and determines the number of processors to be used by repeatedly solving a number of linear programs. The complexity of ITERLP is polynomial in the number of slaves (m) and requires solving  $O(m^3)$  linear programs in the worst case. Though the algorithm is computationally too expensive to be used for a large number of slaves, nevertheless it can be used as a benchmark to compare other heuristic algorithms when obtaining the optimal solution is impractical.

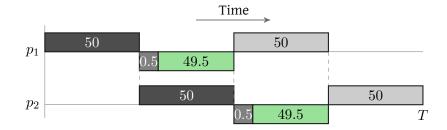

**Condition for Idle Time (Chapter 5)** The idle time theorem proves that under some conditions, idle time may be present in a single processor, but does not specify when the idle time will be present, i.e., under what conditions of the processor communication and computation speeds does it occur. For the first time in DLT, the condition to identify the presence of idle time in a FIFO schedule for two slaves is derived. It has already been proved that there can never be idle time in a LIFO schedule. What is surprising is the simplicity of the condition, and how it is related not only to the communication and computation speeds, but also to the particular divisible load under consideration, specifically to the ratio of size of the result data to the size of input data.

**Condition for Optimality (Chapter 5)** The identification of the limiting condition for the optimality of the FIFO and LIFO schedules for two processors is a significant addition to DLT. This condition shows that even though the presence of idle time depends on the divisible load under consideration, whether LIFO or FIFO is optimal in a two-slave system depends *only on* the communication speeds of the two processors, and the computation speeds do not matter. This condition supports the conclusions drawn by Rosenberg [77] regarding the performance of LIFO and FIFO.

**The concept of** *equivalent processor* (Chapter 5) The equivalent processor concept was used by Bharadwaj et al. [24] to prove a number of results in traditional DLT. It is introduced here for the first time in divisible load scheduling for heterogeneous systems with result collection. The equivalent processor is used to summarize the total processing capacity of a pair of slaves. It enables derivation of a piecewise locally optimal solution to DLSRCHETS by combining two processors into one (virtual) processor at a time.

**The SPORT Algorithm (Chapter 6)** The polynomial-time heuristic algorithm SPORT (System Parameters based Optimized Result Transfer) is another principal contribution of this thesis. The algorithm gives near-optimal solutions to DLSRCHETS and is robust to system

heterogeneity. The SPORT algorithm does not necessarily use all processors and determines the number of processors to be used based on the system parameters (computation and communication capacities). SPORT simultaneously finds the sequence of load allocation and result collection, and the load fractions to be allocated to the processors. Given m processors sorted in the order of decreasing network link bandwidth, the complexity of SPORT is of the order O(m), which is a huge improvement over ITERLP. It is rigorously tested using simulations and its performance is found to be only slightly worse than that of ITERLP.

#### 1.4 THESIS ORGANIZATION

This thesis is organized into five main chapters, preceded by an introduction, and terminated by a conclusion as described below.

**Chapter 1. Introduction** establishes the research context that forms the basis for this thesis. It introduces the application areas of volunteer computing and grid computing, and the problems faced in scheduling applications on these platforms. Next, divisible loads and divisible load scheduling are introduced along with some important results to date. The shortcomings of traditional DLT are enumerated and the research objectives are laid out. The traditional methods are compared with the new approaches in this thesis, and the contributions of this thesis are elaborated. The organization of the thesis is explained.

**Chapter 2. System Model** defines the system model upon which this thesis is built. It explains the various choices made to represent the communication and computation speeds, the model used for size of result data, the assumptions and reasons regarding continuous delivery of data, the unidirectional one-port communication model, and the decision to use linear models of computation and communication time. Models are ultimately approximations of the real systems and are necessary to be able to analyze the system performance without getting caught up in the finer details. It is important to strike the right balance between abstraction and accuracy.

The model proposed is appealing in its simplicity and at the same time, complete in its coverage. The assumptions are well justified for the applications and the environment targeted in the thesis — divisible loads on heterogeneous master-slave platforms. The most important constraints are:

- Communication and computation time is a linearly increasing function of the size of data.

- Size of result data is proportional to the size of allocated input load data.

- Communication and computation cannot overlap a processor can do only one thing at a time.

- A processor can communicate with only one other processor at a time the unidirectional one-port model.

- Data transmission and reception occurs in a single installment non-preemptive or atomic or block-based model.

**Chapter 3. Analysis of DLSRCHETS** provides a detailed derivation of the DLSRCHETS problem definition. After first laying the theoretical basis, the DLSRCHETS problem is defined in terms of a linear program.

This chapter primarily presents the analysis of the optimal solution to DLSRCHETS. Two important proofs are given — one for the allocation precedence condition and the other for the idle time theorem. The allocation precedence condition is necessary to limit the number of possible schedules of DLSRCHETS to a finite number. It argues that there always exists an optimal solution to DLSRCHETS in which the entire load is first distributed to the slaves before the master starts to receive results from the slaves. The proof uses rearrangement of the timing diagram to prove the claim.

The proof of the idle time theorem is a bit more complicated. It uses the geometry of linear programming. A brief introduction to linear programming is also included in the chapter for this reason. The idle time theorem makes a very interesting claim — that not all slaves may be allocated load in the optimal solution, and irrespective of the number of slaves that are allocated load, at most one slave can have idle time in the optimal solution.

The assumption that all processors are allocated load can greatly simplify analysis, but it is not realistic. Instead of making this assumption without justification, the case when all processors are not assumed to be allocated load in the optimal solution is considered. The analysis is not so simple in this case. In linear programming, there is a possibility of some solutions being degenerate. Hence the analysis is carried out for both non-degenerate and degenerate cases. It is proved that the idle time theorem is true for both cases.

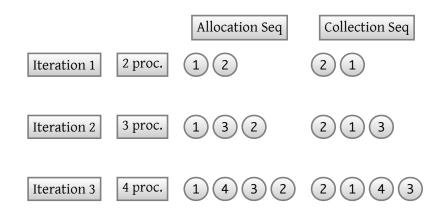

**Chapter 4. The ITERLP Algorithm** proposes the new polynomial-time ITERLP algorithm. The complexity of DLSRCHETS is an open problem and finding the optimal solution is difficult. Thus, one has to resort to heuristic algorithms under the circumstances. The logical approach to solving a combinatorial optimization problem by approximation is *pruning*. That is, to find some criterion that can be used to reduce the number of possible output combinations. The proposed ITERLP algorithm reduces the number of possible allocation and collection sequences to *m* each instead of the usual *m*!. The rationale behind the pruning of possible schedules in ITERLP is explained.

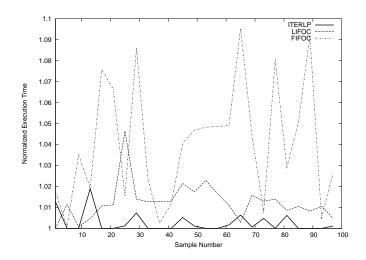

The computation cost of ITERLP is still quite high — in the worst case  $O(m^3)$  linear programs have to be solved. The simulations show that ITERLP performance is much better than LIFO and FIFO over a wide range of parameter values. The performance of the algorithm is quite stable; schedules generated by ITERLP have execution time close to the optimal in most of the cases. In the extensive simulations performed, the maximum deviation of processing time with respect to the optimal is 0.8% for 5 processors, and it takes about 3 to 5 minutes to find the schedule. As the number of processors increase, the time required to compute the solution increases. For example, it takes around 80 minutes to compute the ITERLP schedule for 65 processors. Because the expected error is low, even though computation cost is high, ITERLP allows comparison of other heuristic algorithms when it is impractical to find the optimal solution. A possible hypothesis is offered for the near-optimality of the algorithm.

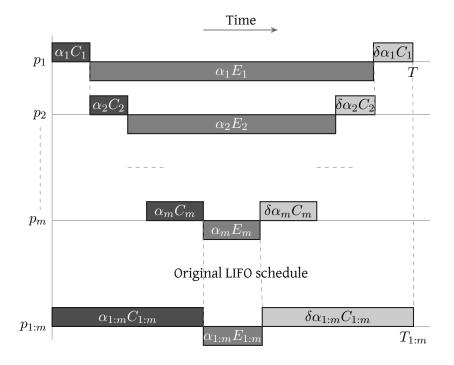

**Chapter 5. The Two-Slave System** lays the foundation of the two-slave system that forms the basis for the SPORT algorithm. Several important concepts are introduced in this chapter as below.

- The three types of possible optimal schedules in a two-slave network and the related derivations.

- Derivation of optimal schedule for two processors using simple if-then clauses and closed-form equations.

- The condition for optimality of the LIFO and FIFO schedules. The result shows that whether LIFO (resp. FIFO) is faster for a two-slave system depends only on the communication speeds of the processor links.

- The condition for the existence of idle time in a FIFO schedule. It shows a relationship between the computation and communication speeds of the two processors and the type of divisible load under consideration.

- Equivalent processor for LIFO and FIFO schedules and related derivations. The equivalent processor enables the combination of two processors into a single virtual processor.

- The extension of the equivalent processor concept to an arbitrary number of processors and its applications. A method to determine the number of processors to allocate load is derived using the equivalent processor concept.

**Chapter 6. The SPORT Algorithm** introduces the SPORT algorithm as a solution to the DLSRCHETS problem. Along with the allocation and collection sequences, the SPORT algorithm finds: (a) the number of processors to use for computation, and (b) the load fractions

to be allocated to the participants. The important point is that this is done without solving time-consuming linear programs. The number of possible allocation and collection sequences is limited to a few, potentially optimal permutations. Because of this, given a set of processors sorted in the order of decreasing communication speed, the complexity of SPORT is O(m), where m is the number of available processors. The algorithm is robust to system composition and it provides good schedules for both homogeneous and heterogeneous types of systems. In the large number of simulations performed, the maximum deviation of processing time with respect to optimal is 1.5% for 5 processors. SPORT is very fast — it takes less than a second to find the solution for 500 processors.

The basic idea behind SPORT is very simple — to use two processors at a time and build a piecewise locally optimal schedule. However it is not very straightforward to be able to do this, and several necessary tools are designed. Detailed explanation regarding the working of the algorithm is given. The method of deriving load fractions using binary tree traversal is explained.

The comprehensive simulation testing of the performance of the algorithms is undoubtedly the highlight of this chapter. SPORT performance is proved to be robust to heterogeneity, number of participants, and value of  $\delta$ . Moreover, this superior performance is obtained at a fraction of the computation time of other algorithms.

**Chapter 7. Conclusion** summarizes the various points covered in the thesis and presents several ideas for future work. It is proposed that future work can proceed in the following main directions:

- 1. Theoretical analysis of complexity and other optimality results,

- 2. Extensions to the current system model,

- 3. Modifying the nature of DLSRCHETS itself, and

- 4. Development of applications and physical testing.

# CHAPTER 2

# THE SYSTEM MODEL

## 2.1 INTRODUCTION

To study and analyze a physical problem, it is necessary to reduce it to its equivalent mathematical form. This is called creating a *model* of the problem, or *modeling* the problem. It is difficult and sometimes unnecessary to capture every aspect of a physical system. The correct level of abstraction to be used, and the parameters to be modeled, depend on the problem under consideration and the purpose of the analysis. Once a correct model is identified, it enables fairly accurate results to be obtained mathematically without having to construct the actual system.

The model used in this thesis to approximate the master-slave system is fairly standard in DLT literature. This chapter explains the various parameters that are used throughout the remainder of this thesis and the reasons behind some of the choices that were made.

#### 2.2 JOB EXECUTION MODEL

This thesis targets divisible loads (also interchangeably called jobs or applications) to be executed on heterogeneous master-slave platforms. The master-slave type of job execution is a popular choice for developing parallel processing applications. For example, the master-slave execution model has been used for image processing and computer vision [25], matrix multiplication problems [48], large genetic database searches [82], image rendering algorithms [95], computational fluid dynamics (CFD) codes [32], Monte Carlo simulations [10], and tree search algorithms [60].

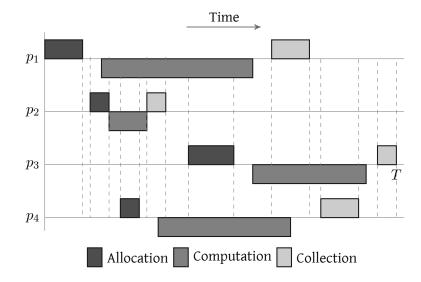

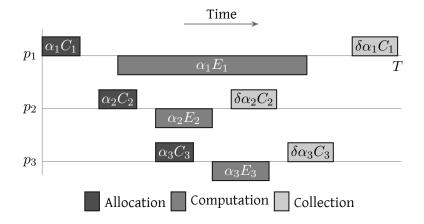

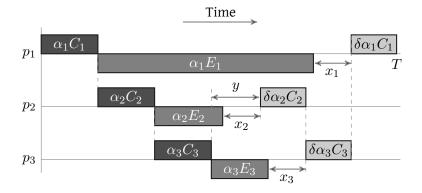

The execution of a divisible job on each slave comprises of three distinct phases in the following order — the allocation phase, where data is sent to the slave from the master, the computation phase, where the data is processed, and the result collection phase, where the slave sends the result data back to the source. The computation phase begins only after

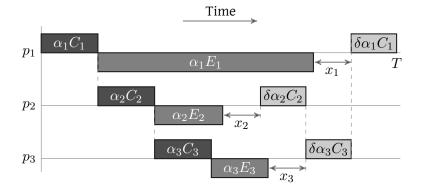

**Figure 2.1** A general schedule for DLSRCHETS. Processors can do only one thing at a time — either compute or communicate. There are three phases for each processor — allocation, computation, and result collection, in that order. However, phases of different processors may be interleaved. Each phase is *atomic*, i.e., continues to its end without interruption. Communication phases (either allocation or collection) cannot overlap as shown by the dashed lines. Computation phases are independent of each other.

the entire load fraction allocated to that slave is received from the source. Similarly, the result collection phase begins only after the entire load fraction has been processed, and is ready for transmission back to the master. This is known as the *non-preemptive, atomic,* or *block based* model, and each phase forms a block on the time line as shown in Fig. 2.1.

## 2.3 COMMUNICATION AND COMPUTATION MODEL

The non-preemptive communication and computation phases necessitate that the slaves are continuously and exclusively available during the course of execution of the divisible load, and have sufficient buffer capacity to receive the entire load fraction in a single installment from the master. Traditionally, DLT has used the single installment delivery of data. Banino et al. [8] and Beaumont et al. [14] considered a multi-installment strategy. The data is considered to be split into equal sized tasks, and the maximum number of tasks that can be delivered to the processors in a given time interval is found. They argue that in the *steady state*, separate modeling of result collection is unnecessary. They concluded that allocation should proceed in the order of decreasing communication bandwidth for optimal performance in the steady-state.

In this thesis, the focus is on the more traditional form of single-installment DLS on account of the following reasons:

- To get a better understanding of the underlying problem structure when result collection and node heterogeneity are considered together.

- The scheduling of tasks is essentially left to chance in the multi-installment strategy. Collisions during communication are likely to cause delays.

- For certain applications, multi-installment distribution of data is difficult or not desirable.

All processors (master as well as slaves) follow a *unidirectional single-port* communication model, and a *no-overlap* computation model. That is, master and slaves can do only any one thing at a time — either communicate or compute (the no-overlap model), and if communicating, then either send data or receive data (the unidirectional one port model). During communication between the master and slave, both are kept busy for the entire duration of the transmission. This model is well accepted and has been used in most of the papers in this area [9, 11–13, 22–26, 34, 36, 57, 74, 84, 85], just to cite a few.

A few papers have considered DLS with a *multi-port* model for the master [54, 70, 103, 104]. If it is possible to have as many ports as there are slaves, and also be able to program the source to communicate simultaneously with all the slaves, then the problem of sequencing allocation and result collection becomes irrelevant.

The unidirectional single-port model is used in this thesis for the following reasons:

- Traditionally, DLT has used the unidirectional single-port (sequential) communication model, as evidenced by the large body of literature using this model mentioned above and in Chapter 1 versus the few papers [54, 70, 103, 104] cited above for the multi-port model.

- As mentioned in Chapter 1, this thesis addresses DLS on generic heterogeneous systems such as volunteer and grid computing platforms. The master-slave topology is an application-level *logical construct* on these systems. The source is not a special machine as used in the papers [54, 70, 103, 104] cited above, but can be any machine that wants to participate in the computation.

- An experimental setup such as the one described in [16, 18] using MPI (Message-Passing Interface) to implement the master-slave processing follows the unidirectional single-port model as it is found to be more realistic in practice. As noted in [92], *scatter-gather* operations in MPI need to be improved before it can be reliably used for simultaneous data transfer to and from several slaves.

- If each slave was to be connected to the master by a dedicated link (port), then the number of slave processors that could be used would be seriously limited as it is not

practical to have a large number of physical ports on a computer.

# 2.4 COMMUNICATION AND COMPUTATION PARAMETERS

These days there is an almost endless variety of computers available. Computers can differ in almost every aspect – right from the low motherboard interconnection bus level to the high OS (operating system) level, and everything else in between including the CPU type, CPU speed, CPU quantity, CPU on board cache memory, size of RAM, hard disk space, auxiliary processors, to name just a few features. Thus, if one were to truly model heterogeneity, the feature vector of differentiation would be large.

However, in a master-slave system, from the master's point of view, observing the performance of an application on a slave, it is not necessary to model most of the features mentioned above. This is because, even though each feature affects the performance of the application to a certain extent, it does not help the master to know how that happens. The master has to finish a certain task in the minimum amount of time, so all it really needs to know is how much time will it take for a slave to process the task, so that the master can decide whether or not to allocate that task to that particular slave. The processing time of a task on a slave includes the time to send the relevant data to the slave, the time for the slave to carry out the requisite computation on the data, and the time required to receive the result data from the slave once the computation is complete.

Thus, even though the slaves may actually differ in a number of ways, as far as the master is concerned, the heterogeneity manifests itself only in the different time it takes to communicate and receive data from the slaves, and for the slaves to compute the results. Hence a master-slave network can be characterized in terms of the communication and computation speeds (times) of its components.

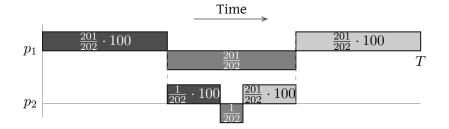

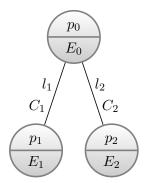

A heterogeneous master-slave (sometimes called as *star* or *single-level tree*) system  $\mathcal{H} = (\mathcal{P}, \mathcal{L})$  is as shown in Fig. 2.2, where  $\mathcal{P} = \{p_0, \ldots, p_m\}$  is the set of m + 1 processors, and  $\mathcal{L} = \{l_1, \ldots, l_m\}$  is the set of m network links that connect the master scheduler (source)  $p_0$  at the center of the star (root of the tree), to the slave processors  $p_1, \ldots, p_m$  at the points of the star (leaves of the tree).  $\mathcal{E} = \{E_1, \ldots, E_m\}$  is the set of unit computation times of the slave processors, and  $\mathcal{C} = \{C_1, \ldots, C_m\}$  is the set of unit communication times of the network links, i.e.,  $p_k$  takes  $E_k$  time units to process a unit load transmitted to it from  $p_0$  in  $C_k$  time units over the link  $l_k$ . It follows that  $E_k, C_k > 0, k \in \{1, \ldots, m\}$ . The values in  $\mathcal{E}$  and  $\mathcal{C}$  are assumed to be deterministic and available at the master.

The master holds a divisible load (job)  $\mathcal{J}$  that is to be distributed and processed on  $\mathcal{H}$ . Based on the unit communication and computation time values of the slaves, the master  $p_0$  splits  $\mathcal{J}$  into parts (fractions)  $\alpha_1, \ldots, \alpha_m$  and sends them to the respective slave pro-

**Figure 2.2** The heterogeneous master-slave system  $\mathcal{H}$ . The processors have different computation speeds and network bandwidths.

cessors  $p_1, \ldots, p_m$  for computation. Each such set of m fractions is known as a *load distribution*  $\alpha = \{\alpha_1, \ldots, \alpha_m\}$ . The source does not retain any part of the load for computation. Since the job  $\mathcal{J}$  is assumed to be arbitrarily divisible,  $\alpha_k \in \mathbb{R}^+_0$ ,  $\alpha_k \ge 0$ ,  $k \in \{1, \ldots, m\}$ .

The unit communication and computation times are conditional upon the job  $\mathcal{J}$  under consideration. So ideally, the values should be indexed as  $C_k^{\mathcal{J}}$  and  $E_k^{\mathcal{J}}$ , to indicate that the values are valid only for the job  $\mathcal{J}$ . In this thesis, this index is omitted as the context of analysis and discussion is always clear to be the job  $\mathcal{J}$ .

### 2.5 RESULT DATA MODEL

For the divisible loads under consideration, such as image and video processing, Kalman filtering, matrix conversions, etc., the computation phase usually involves simple linear transformations on the input data, and the volume of returned results can be considered to be proportional to the amount of load received in the allocation phase. If the allocated load fraction is  $\alpha_k$ , then the returned result is equal to  $\delta \alpha_k$ . The constant  $\delta$  is application specific, and is the same for all processors for a particular load  $\mathcal{J}$ . This is the accepted model for returned results in literature to date [1, 9, 16–18, 24, 36, 77, 104]. In this thesis, it is assumed that  $0 \leq \delta \leq 1$ .

#### 2.6 COMMUNICATION AND COMPUTATION TIME

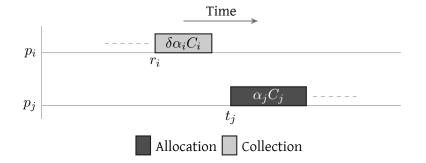

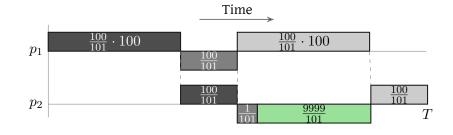

The time taken for communication and computation is assumed to be a linearly increasing function of the size of load fraction. For a load fraction  $\alpha_k$ ,  $\alpha_k C_k$  is the transmission time from  $p_0$  to  $p_k$ ,  $\alpha_k E_k$  is the time it takes  $p_k$  to perform the requisite processing on  $\alpha_k$ , and  $\delta \alpha_k C_k$  is the time it takes  $p_k$  to finally transmit the results back to  $p_0$ .

Though a linear model is considered for computation and communication times for

the sake of simplicity, all results can be easily extended to other (e.g. affine) cost models. For example, the computation time and the load allocation time of a processor  $p_k$  can be defined as  $e_k(\alpha_k)$  and  $c_k(\alpha_k)$ , where  $e_k(\cdot)$  and  $c_k(\cdot)$  are functions of the allocated load fraction  $\alpha_k$ . Similarly, the size of result data can be an application-dependent function  $d_{\mathcal{J}}(\cdot)$  of  $\alpha_k$ , giving a result collection time  $c_k(d_{\mathcal{J}}(\alpha_k))$  for a processor  $p_k$ .

The functions  $c_k(\cdot)$ ,  $e_k(\cdot)$ , and  $d_{\mathcal{J}}(\cdot)$  are concave, monotonically non-decreasing functions of  $\alpha_k$ . This category of functions includes all non-decreasing linear, affine, and constant functions. The concave non-decreasing nature ensures that the communication or computation time of a slave for a larger load fraction is always greater than the time for a smaller load fraction. In this thesis,  $c_k = \alpha_k C_k$  and  $e_k = \alpha_k E_k$  are linear functions, while  $d_{\mathcal{J}} = \delta$  is a constant function.